상태 레지스터는 최근 계산한 수학 연산 명령에 대한 정보를 가지고 있습니다. 연산 명령 정보는 조건부 연산을 수행하기 위해, 프로그램 플로우를 변경하는 데에 사용될 수 있습니다. 상태 레지스터는 ALU 연산 이후 업데이트됩니다. 많은 경우에서 비교 명령 사용을 줄일 수 있어 결과적으로 빠르고 컴팩트한 코드를 만들 수 있습니다.

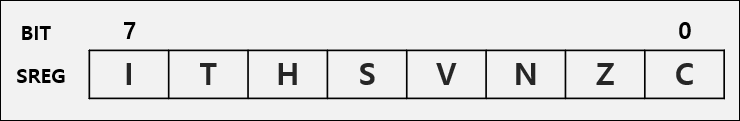

상태 레지스터(SREG)

상태 레지스터란 ALU가 가장 최근 실행한 산술 명령의 결과와 상태를 표시하는 레지스터입니다. 하드웨어에 의한 ALU 동작이 끝난 후 SREG가 업데이트됩니다. 상태 레지스터의 값을 통해 다음 목적으로 사용됩니다.

- 상태 레지스터의 BIT값을 통한 연산 결과 확인

- 프로세서의 상태를 알아내거나 흐름을 변경하는 데 계산 결과 사용

각 BIT별 설명은 아래와 같으며 아래 상황에 따라 BIT가

- BIT 7 : I (Global Interrupt Enable)

Global Interrupt Enable Bit는 인터럽트 인가를 위해 반드시 Set이 되어야 된다. 개별 인터럽트는 각각 개별 제어 레지스터에서 실행된다. Global Interrupt Enable 레지스터가 클리어 되면, 개별 인터럽트 여부와 상관 없이 개별 인터럽트 모두 인가되지 않는다.

- BIT 6 : T (Copy Storage)

Bit Load (BLD)와 Bit Store (BST)는 T-bit를 동작한 bit 목적지 또는 소스로 사용한다. 레지스터 내 레지스터 비트가 BST 명령에 의해 T-bit에 복사될 수 있다. 그리고 T-bit는 레지스터 비트에 BLD 명령에 의해 복사될 수 있다.

- BIT 5 : H (Half Carry Flag)

일부 수학 연산에서 a half carry를 표시한다. Binary Code Deicmal 연산에 유용하다.

- BIT 4 : S (Sign Flag, S = N xor V)

N-bit(음수 플래그)와 V-bit(2의 보수 오버플로우 플래그) XOR 조건으로 Set된다.

- BIT 3 : V (Two's Compliment Overflow Flag)

2의 보수 오버플로우 플래그이다.

- BIT 2 : N (Negative Flag)

수학 연산이나 논리 연산에서 음수 결과를 표시한다.

- BIT 1 : Z (Zero Flag)

수학 연산이나 논리 연산에서 0 결과 값을 표시한다.

- BIT 0 : C (Carry Flag)

수학 연산이나 논리 연산에서 자리 올림을 표시한다.

'임베디드소프트웨어' 카테고리의 다른 글

| AVR 디지털 입력/출력 포트의 모든 것 (정의, 설정, 구성 확인) (0) | 2022.03.23 |

|---|---|

| 8-Bit AVR 스택(Stack) 살펴보기 (0) | 2022.03.22 |

| AVR 명령 타이밍, 계산 수행 과정 (0) | 2022.03.21 |

| 8-Bit AVR 코어 살펴 보기 (레지스터, ALU, 메모리, 인터럽트) (0) | 2022.03.20 |

| AVR 마이크로프로세서의 메모리 (0) | 2022.03.17 |

댓글